BJT CE

Amp with QUCS, Lab

Part I. Simulation

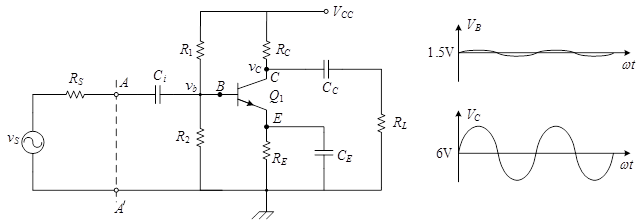

Figure: BJT CE amp

vs = 1 kHz, zero offset, 100 mVpp with A-A' terminal open-circuited

Rs = 50 Ω, Ci =

0.1 μF, R1 = 200 kΩ, R2

= 33 kΩ, RC = 4.7

kΩ

RE = 750 Ω, CE

= 1 μF, CC = 0.1

μF, RL = 10 kΩ, Q1 = 2SC945, VCC = 12 VDC

QUCS 프로그램 다운로드 및 설치

https://sourceforge.net/projects/qucs/files/qucs-binary/

1. DC simulation (bias voltage displayed on the schematic)

2. Transient simulation (input and ouptput voltages vs time)

3. Voltage transfer function (voltage gain vs frequency)

4. Current transfer function (current gain vs frequency)

Part II. Theory

1. CE(common emitter) amplifier (공통 이미터 증폭기)의 특징

- 용도: 저주파 전압증폭, RF 트랜시버, 저잡음증폭기

- 특징:

입력임피던스 = Low, 출력임피더스 = High, 전력/전압/전류이득 = High

주파수특성: 고주파에서 동작하지 않음.

전압이득: 불안정(온도변화)

2. CE 증폭기 동작원리

1) DC 바이어스:

- 베이스-이미터 접합 = 순방향 바이어스

- 베이스-컬렉터 접합 = 역방향 바이어스

- 컬렉터 정압: Vcc의 약 1/2. 선형성을 유지하면서 출력전압의 크기를 최대로 하기 위해

- R1, R2,

RE는 베이스 DC 바이어스 전류 결정

2) AC 증폭

- 커플링 커패시터(Ci,

Cc): 신호 주파수에서 매우 낮은 임피던스 (단락으로 취급)

- 신호전압 vs에 비례하여 베이스 전류 ib 변화가 크게(50-200배) 증폭되어 컬렉터 전류 ic 로 흐름.

- 컬렉터 전류의 일부가 RL에 흘러서 출력전압으로 나타난다.

- 이미터 커패시터 CE는 이미터 저항에 의한 이득저하를 감소시킴.

3. CE 증폭기 DC바이어스 해석

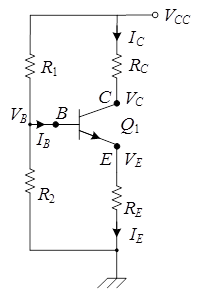

그림: CE 증폭기 바이어스 해석

- 베이스-이미터 접합: 순방향 바이어스. 전압제어 전류증폭

- 베이스-컬렉터 접합: 역방향 바이어스

- DC 회로: 전체 증폭기 회로에서 커패시터로 연결된 선로를 제거

- 회로이론 적용 IB공식 유도:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

- 트랜지스터: DC 공식 적용

![]()

![]() = 120-200 @ IC

= 0.02-2 mA (2SC945 데이터시트로부터)

= 120-200 @ IC

= 0.02-2 mA (2SC945 데이터시트로부터)

Use ![]() = 200 @ IC

= 1 mA

= 200 @ IC

= 1 mA

![]()

![]()

![]()

![]()

![]()

![]()

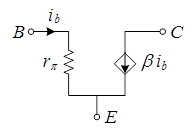

4. BJT 증폭기 교류 해석

- 간략한 교류 등가회로 사용

그림: BJT의 간략한 교류 등가회로

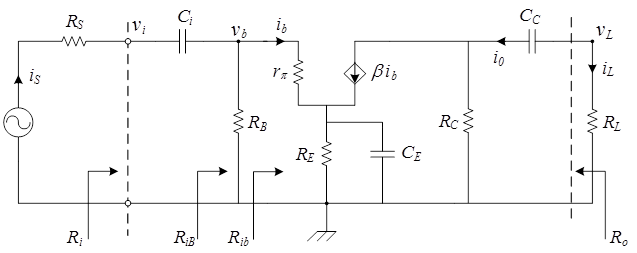

1) 커패시터를 포함한 해석

그림: BJT CE 증폭기

full equivalent circuit

![]() (for 2SC945 트랜지스터)

(for 2SC945 트랜지스터)

![]()

![]()

![]()

![]() (input impedance)

(input impedance)

![]()

![]()

![]()

![]()

![]()

![]() (voltage gain)

(voltage gain)

![]()

![]() (current gain)

(current gain)

Output impedance: ![]()

![]()

위 수식을 프로그래밍하여 계산:

![]()

![]()

![]()

![]()

![]()

![]()