실험07 - 발진회로, 이론

I. Theory

1.1 발진기 기초

ㅇ 발진기 (oscillator)

– 정현파 (sine wave) 또는 구형파 (rectangular wave)를 발생하는 장치

– 발진기 용도: 통신용 신호원, 디지털회로의 클록생성, 함수발생기 신호원

ㅇ 발진기의 주파수별 분류

– 저주파 발진기 (LFO; low-frequency

oscillator): < 20 Hz

– 오디오 발진기: 16 Hz – 20 kHz

– RF 발진기: 100 kHz – 100 GHz

ㅇ 발진기 종류별 최대 발진 주파수

– Wien-bridge oscillator: most popular up to 1 MHz

– Phase-shifte oscillator: up to 200 – 300 kHz

– LC oscillator: up to millimeter-wave

– Cystral oscillator: up to 100 MHz

1.2 Feedback 발진기 이론

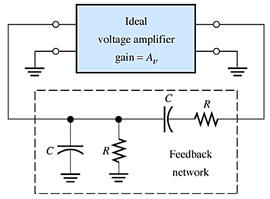

1)

Negative feedback

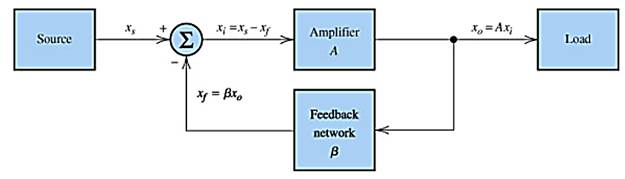

그림: Feedback circuit block diagram [Kurssit]

–

Negative feedback: 출력신호의 일부를 추출하여 입력신호에서 빼준다. 출력신호가 증가하면 빼주는 신호도 커지므로 출력신호의 변화를 억제

–

출력신호의 β배 한 후에 입력신호로부터 빼준다.

–

출력이 증가하면 입력신호가 감소하여 출력증가를 방지한다.

–

Negative feedback: Aβ > 0

–

다음 식으로 주어지는 안정적인 출력이 발생. 증폭기 안전화 회로에 이용

![]()

2) Positive feedback

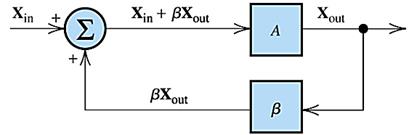

그림: Positive feedback [Kurssit]

– Positive feedback: 출력 신호의 일부를 추출하여 입력신호에 더해 준다. 출력신호가 증가하면 입력에 더해주는 신호가 증가하여 출력신호는 더욱 증가. 출력신호는 포화값까지 증가

– 위 그림에서 궤환신호 ![]() 을 입력에 더해 줄 경우

을 입력에 더해 줄 경우

![]()

–

입력신호 xi = 0인 경우에도 신호가 나오려면 다음 조건 만족 필요

![]() : Barkhausen 조건 (불안정 조건, 발진기에 적용)

: Barkhausen 조건 (불안정 조건, 발진기에 적용)

최초: ![]()

최종: ![]()

2. Wien-bridge 발진기

– Wien: 발음 veen

2.1 Wien brige 회로

– 1891년Max Wien이 고안

–

용도: 커패시턴스 측정, Notch filter in harmoni distortion analyzers,

Frequency discriminating elements in HF oscillators

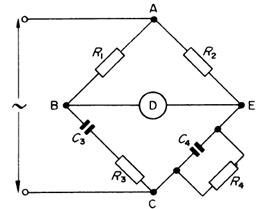

그림: Wien bridge를 이용한 커패시터 측정 [Gregory]

Gregory, An Introduction to Electrical Instrumentation and Measurement

Systems, 2nd Ed.,

![]()

![]() : 브리지 평형조건

: 브리지 평형조건

![]()

![]() (1)

(1)

![]() (2)

(2)

(1), (2) 동시 만족해야 한다.

![]() 를 조정: 식 (2)의 공진주파수 튜닝

를 조정: 식 (2)의 공진주파수 튜닝

![]() : 식 (1)의 소자값 비율 튜닝

: 식 (1)의 소자값 비율 튜닝

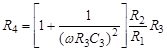

– 브리지가 평형을 이룬 경우

![]()

![]()

: C4에 손실이 있는 경우R4에C4의 등가병렬저항 포함

: C4에 손실이 있는 경우R4에C4의 등가병렬저항 포함

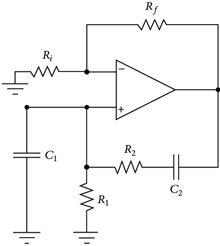

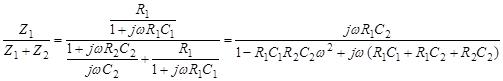

2.2 Wien bridge를 이용한 발진기 주파수 선택회로

![]()

![]()

![]()

그림: 발진기 예제 [Kurssit]

2.3 Wien-bridge 발진기

그림: Wien-bridge 발진기

– Loop gain:

![]()

A0 : 증폭기 이득

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

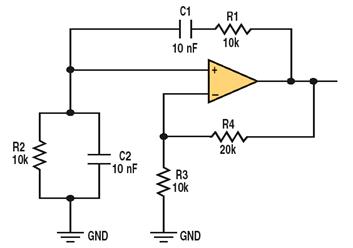

ㅇWien-bridge 발진기 예

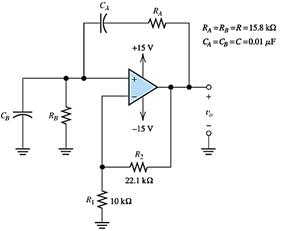

그림: 1.59 kHz Wien-bridge 발진기 [Stack Exchange]

2.4 Wien-bridge 발진기의 진폭 안정화

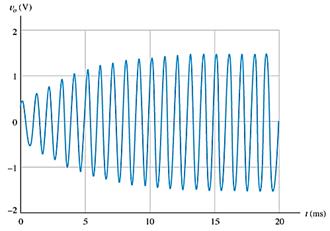

1) 발진기 출력 클리핑

– Wien bridge 발진기의 진폭을 제어하지 않으면 bias rail에 가깝게 증가하여 클리핑 됨.

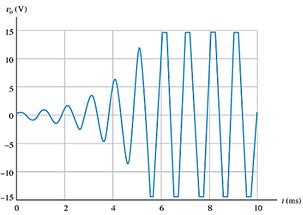

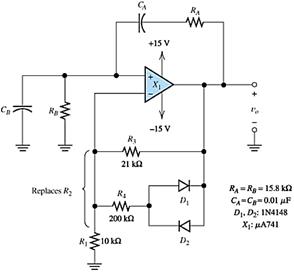

그림: 1

kHz Wieng-bridge 발진기와 출력파형. 증폭기 이득이2.21이 되어 출력이 클리핑 됨 [Kurssit]

2) 출력 클리핑 방지방법

– 증폭기의 closed loop gain을 미세하게 조정

–

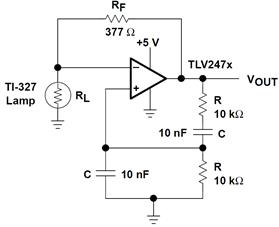

피드백 저항 ![]() 로 백열전구 사용: Heacham (1938), Hewlett. 출력전압이 증가하면 백열전구의 전류가 증가하고 전류증가에 따라 백열전구 저항 증가하여 출력전압 증가를 억제

로 백열전구 사용: Heacham (1938), Hewlett. 출력전압이 증가하면 백열전구의 전류가 증가하고 전류증가에 따라 백열전구 저항 증가하여 출력전압 증가를 억제

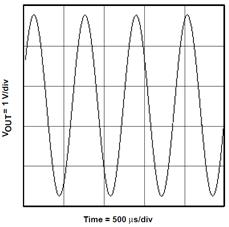

그림: 백열전구를 이용한 Wien-bridge 발진기 진폭 안정화. 출력왜곡율은0.1% 이하 [Texas Instruments]

그림: 다이오드를 이용한 Wieng-bridge 발진기 진폭 안정화 [Kurssit]

–

증폭기 이득을 결정하는 피드백 저항에 다이오드, 써미스터, FET, photocell과 같은 비선형 소자를 사용하여 발진기 진폭 안정화 가능

–

왜곡율의0.0003% (3 ppm)이하인 발진기 설계 가능 [Wikipedia]