정보통신실험

05주 - 연산 증폭기

실험

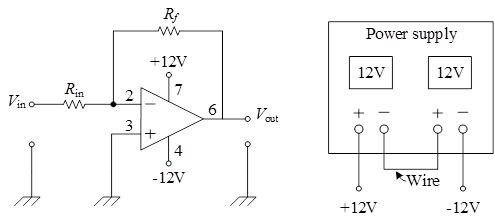

1. 반전 증폭기

1) 실험회로 구성

Vin = 0.1 VDC ; Rin = 1k, Rf = 10 k

Op amp = LM741; +Vs = +12 VDC; -Vs = -12 VDC

ㅇ 주의사항

- 연산증폭기에 전원인가시 Ground (0V) 단자가 없음.

- 단뱡항 전원인가시 전원공급기의 0V 단자는 회로의 Ground에 연결

- 양방향 전원인가시 전원공급기 (+) (-) === (+) (-)와 같이 2채널 전원 중 왼쪽 채널의 (-) 단자를 오른쪽 채널 (+) 단자와 도선으로 연결하고 왼쪽 채널 (+) 단자를 연산증폭기의 +Vcc 단자에 연결, 오른쪽 채널 (-) 단자를 연산증폭기의 -Vcc 단자에 연결

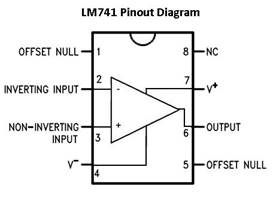

ㅇ LM741 연산증폭기 자료

- Pin-out

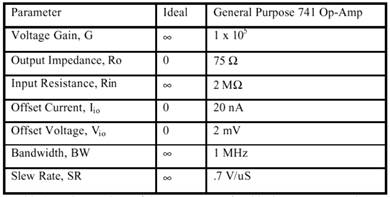

- LM741 연산증폭기 Specifications (특성표)

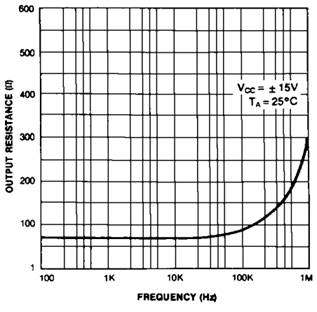

- LM741 증폭기

출력임피던스

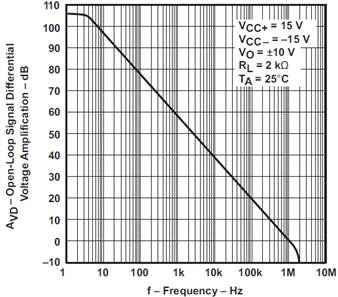

- LM741 연산증폭기의 Open-loop Gain

2) 저항값 측정

Rin = (

) kΩ, Rf = (

) kΩ

3) 전압이득 측정

Vin = (

) V , Vout = (

) V

전압이득 = Vout/Vin = (

)

4) 입력저항 측정

Vin = (

) V, Iin = (

) mA

Rin = Vin/Iin (측정값) = (

) kΩ

Rin = Vin/Iin (이론값) = (

) kΩ

5) 출력저항 측정

Vout (open-cicuit) =

(

) VDC, Iout

(short-circuit) = (

) mA

Rout = Vout/Iout (측정값) = (

) Ω

Rout = RoA || Rf (이론값) = (

) Ω

6) 주파수 특성 측정

Vin = 0.2 Vac

(peak-to-peak), 주파수: 1k, 10k, 100k, 1M, 10M Hz

|

f

(Hz) |

1k |

10k |

100k |

1M |

10M |

|

Vin VAC(pp) |

|

|

|

|

|

|

Vout VAC (pp) |

|

|

|

|

|

|

Av (voltage gain) |

|

|

|

|

|

|

이론값 |

|

|

|

|

|

2. 가산 증폭기

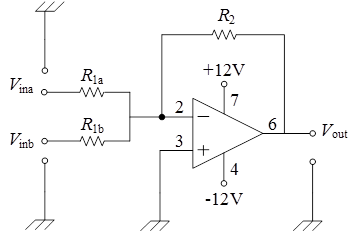

1) 회로 구성

Op amp = LM741; +Vs = +12 VDC; -Vs = -12 VDC

R1a = 10k, R1b = 10k, R2 = 20k

Vina = TTL square wave, 0-3.61V, 주파수 1kHz (함수발생기의 TTL 출력은 주파수만 조정가능)

Vinb = Sine wave, 2.5 Vpp (peak-to-peak)(함수발생기 설정), 주파수 1kHz, Offset = 0, Phase = 90° (sine 함수 파형이 왼쪽으로 1/4 주기 이동)

(참고) 함수발생기 파형 진폭을 2.5Vpp로 설정한 경우 출력에 50Ω이 연결된 경우 2.5Vpp, 10kΩ/10MΩ과 같이 큰 저항 연결시 5.0Vpp

2) Vina, Vinb 파형 동시 측정

3) Vina, Vout파형 동시 측정

4) 다음 표 완성 (T = 1 / f), T+/2 = right after

T/2, T- = right before T

|

t |

0 |

T/4 |

T+/2 |

3T/2 |

T- |

|

Vina + Vinb |

|

|

|

|

|

|

Vout, meas. |

|

|

|

|

|

|

Vout, theory |

|

|

|

|

|