정보통신실험

05주 - 연산 증폭기

시뮬레이션

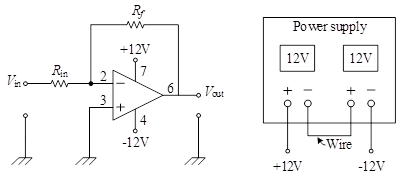

1. 반전 증폭기

1) 회로 구성

Vin = 0.1 VDC ; Rin =

1k, Rf = 10 k

Op amp = LM741; +Vs =

+12 VDC; -Vs = -12 VDC

2) RL (Vout 단자에 연결) = 1000 k = 1 M로 하고 회로에 DC 전압과 DC 전류가 표시되게 하라.

3) 전압이득을 구하라.

4) 입력저항을 구하라.

5) RL (Vout 단자에 연결) = 0.001로 하고 회로에 DC 전압과 DC 전류가 표시되게 하라.

6) 출력저항을 구하라.

7) Vin = 0.2 Vpp, f = 1 kHz로 하고 입력전압과 출력전압을 동일한 그래프에 도시하라.

8) Vin = 0.2 Vpp, f = 1 k, 10 k, 100 k, 1 M, 10 MHz로 하여 다음 표를 완성하라.

|

f

(Hz) |

1k |

10k |

100k |

1M |

10M |

|

Vin (Vpp) |

|

|

|

|

|

|

Vout (Vpp) |

|

|

|

|

|

|

Vout phase delay |

|

|

|

|

|

|

|Av| (voltage gain), simul. |

|

|

|

|

|

|

|Av|, theory |

|

|

|

|

|

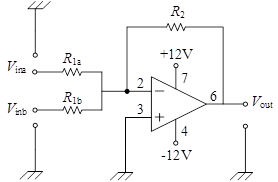

2. 가산 증폭기

1) 회로구성

Op amp = LM741; +Vs = +12 VDC; -Vs = -12 VDC

R1a = 10k, R1b = 10k, R2 = 20k

Vina = TTL square

wave, 펄스진폭 3.36V, 주파수 1kHz, duty 50%

Vinb = Cosine wave, 5.0 Vpp (peak-to-peak), 주파수 1kHz, Offset = 0, Phase = 0°

2) Vina, Vinb 파형 같은 그래프에 도시

3) Vina, Vout을 같은 파형에 도시

4) 다음 표 완성 (T = 1 / f), T+/2 = right after

T/2, T- = right before T

|

t |

0 |

T/4 |

T+/2 |

3T/2 |

T- |

|

Vina + Vinb |

|

|

|

|

|

|

Vout, meas. |

|

|

|

|

|

|

Vout, theory |

|

|

|

|

|

3. 회로 시뮬레이션 결과 (예시)

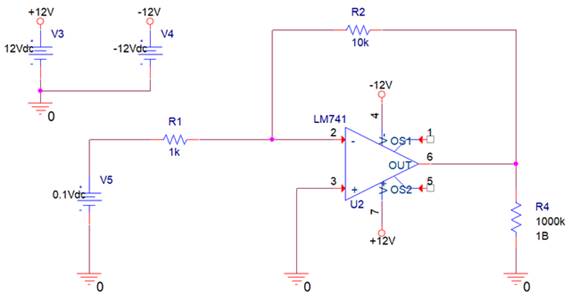

3.1 반전 증폭기

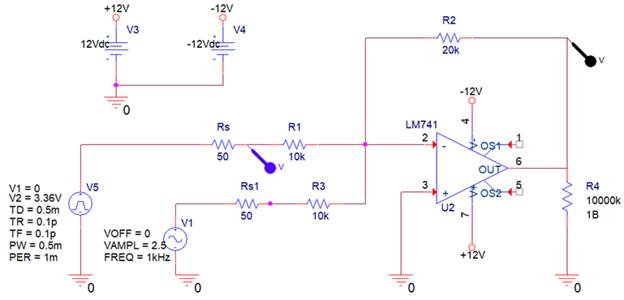

1) 회로 구성

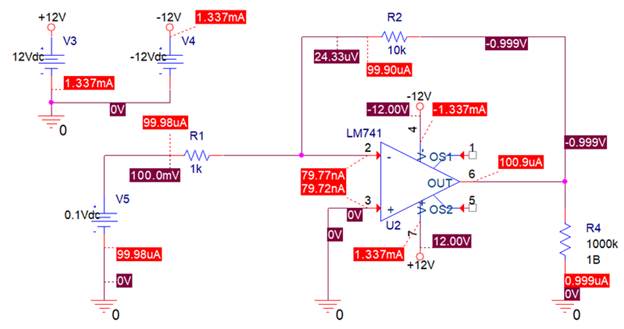

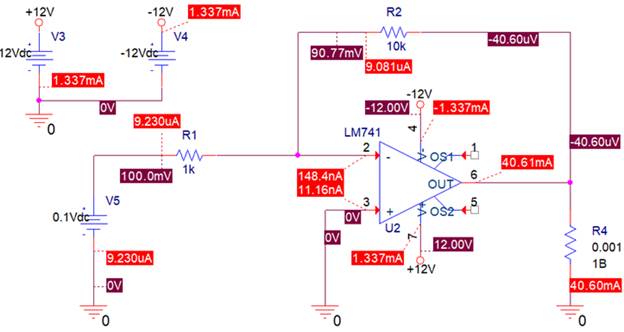

2) RL (Vout 단자에 연결) = 1000 k = 1 M로 하고 회로에 DC 전압과 DC 전류가 표시되게 하라.

3) 전압이득을 구하라.

Vin = (

0.1 )

VDC , Vout = ( -0.999

) VDC

전압이득 = Vout/Vin = ( - 9.99 )

4) 입력저항을 구하라.

Vin = ( 0.1 )

VDC, Iin = ( 0.09998 ) mA

Rin = Vin/Iin (측정값) = ( 1.0002 )

kΩ

Rin = Vin/Iin (이론값) = (

Rin = 0.984 ) kΩ

5) RL (Vout 단자에 연결) = 0.001로 하고 회로에 DC 전압과 DC 전류가 표시되게 하라.

6) 출력저항을 구하라.

Vout (open-cicuit) =

( -0.999 ) VDC, Iout (short-circuit) = ( -40.61

) mA

Rout = Vout/Iout (측정값) = ( 24.6 ) Ω

Rout = RoA || Rf (이론값) = (

75 || 10k = 74.4 )

Ω

(오차원인) 741 연산증폭기의 출력저항이 25Ω으로 추측됨.

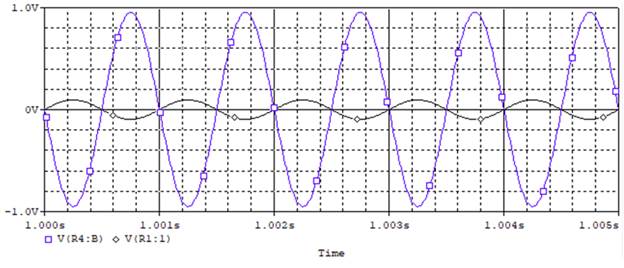

7) Vin = 0.2 Vpp, f = 1 kHz로 하고 입력전압과 출력전압을 동일한 그래프에 도시하라.

8) Vin = 0.2 Vpp, f = 1 k, 10 k, 100 k, 1 M, 10 MHz로 하여 다음 표를 완성하라.

|

f

(Hz) |

1k |

10k |

100k |

1M |

10M |

|

Vin (Vpp) |

0.19 |

0.19 |

0.195 |

0.2 |

0.2 |

|

Vout (Vpp) |

1.90 |

1.88 |

1.382 |

0.132 |

0.00534 |

|

Vout phase delay |

0° |

7.2° |

54° |

108° |

173° |

|

|Av| (voltage gain), simul. |

10 |

9.9 |

7.1 |

0.66 |

0.0267 |

|

|Av|, theory |

10 |

10 |

10(18/20) =7.9 |

10(0/20) =1 |

N/A |

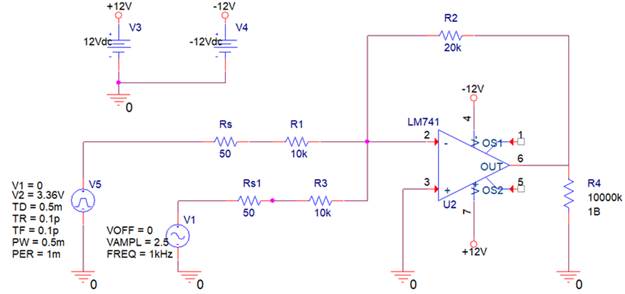

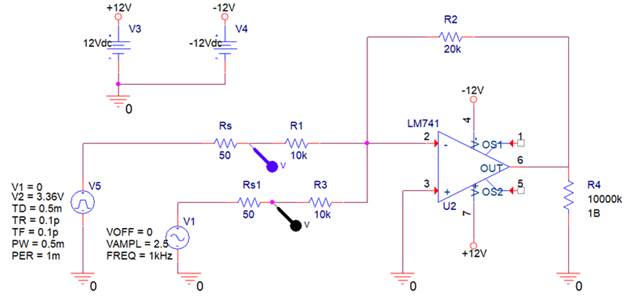

333333333333333.2 가산 증폭기

1) 회로구성

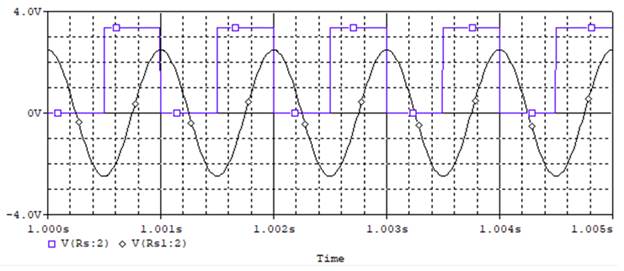

2) Vina, Vinb 파형 같은 그래프에 도시

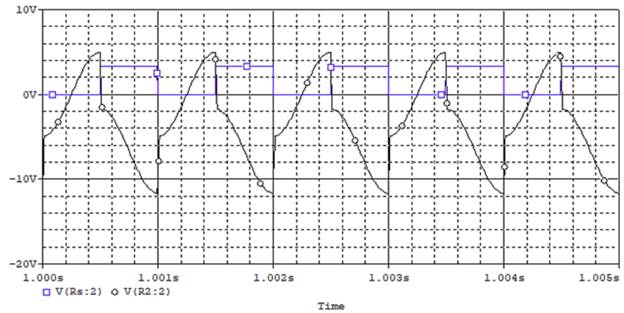

3) Vina, Vout을 같은 파형에 도시

4) 다음 표 완성 (T = 1 / f), T+/2 = right after

T/2, T- = right before T

|

t |

0 |

T/4 |

T+/2 |

3T/2 |

T- |

|

Vina + Vinb |

2.5 |

0 |

0.7 |

3.2 |

5.7 |

|

Vout, meas. |

-5.0 |

0 |

-1.7 |

-6.5 |

-10.3 |

|

Vout, theory |

-5.0 |

0 |

-1.4 |

-6.4 |

-11.4 |